Latch-Up 2023 is a Go!

The FOSSi Foundation is proud to announce Latch-Up, a conference dedicated to free and open source silicon, to be held over the weekend of Friday, March 31 to Sunday, April 2, 2023 in Santa Barbara, California, USA.

Latch-Up is a weekend of presentations and networking for the open source digital design community, much like its European sister conference ORConf. The 2019 Latch-Up in Portland was a stellar success, but the global pandemic led to the cancellation of the planned Cambridge, MA Latch-Up in 2020.

We're thrilled that we're now able to launch Latch-Up once again, and have opened the call for sponsors - with the call for participation to follow in the coming weeks. So save the date, register to attend, and we encourage you to submit a presentation or proposal if you have a project or idea on the topic to share!

Questions? Visit the website for more information, or ping the organizers via @LatchUpConf on Twitter or email.

-Philipp Wagner, Director, FOSSi Foundation

The FOSSi Foundation Prepares for Google Summer of Code 2023

Google has announced the 19th consecutive Google Summer of Code (GSoC), a programme which pairs student coders with mentors from industry and academia to work on open-source initiatives - but this time it's not exclusive to student participants.

"For 2023, we are expanding the programme to be open to students and to beginners in open source software development," Google's Stephanie Taylor and Perry Burnham explain. "GSoC’s mission of bringing new contributors into open source communities is centered around mentorship and collaboration."

Participants working with the FOSSi Foundation as part of GSoC 2022 worked on projects as diverse as a development framework for the Open MPW Shuttle programme which seeks to put free and open-source silicon projects into small-scale production to a graphical waveform viewer for the terminal, from multi-core RISC-V designs to accelerator kernels for FPGAs.

Where previous years have focused on accredited students, however, GSoC 2023 will be casting a wider net. Interested parties can find out more and how to apply on the GSoC website - and the FOSSi Foundation will be announcing its slots as an umbrella organisation as soon as they are confirmed.

Verilator 5 Takes the First Steps Towards Non-Synthesisable Verilog Subset Support

The Verilog project has announced a "major new release," Verilog 5, which brings a range of new features, enhancements, and usability improvements - along with progress towards the support of non-synthesisable Verilog.

"Previously, Verilator was mostly limited to synthesisable Verilog code," explains FOSSi Foundation director Philipp Wagner. "With the 5.000 release, the first major steps towards the non-synthesizable Verilog subset are taken (as they are required, e.g., to run UVM testbenches)."

Among the new features of Verilator 5 are a redesign of the scheduling system to allow for more correct generation and simulation of advanced clocks, the ability to enable or disable support for timing constructs including event controls and wait statements, and a new combinatorial logic optimiser which can considerably improve performance for many large designs.

The new release also brings with it gains for usability, Philipp explains, "making it as simple to use Verilator as many other simulators. Users don't need to write a C++ wrapper for their Verilog design - Verilator can now generate one on its own."

More details on Verilator 5 are available in the GitHub announcement; the project itself is available on GitHub under the reciprocal GNU Lesser General Public Licence 3.

Anton Blanchard's Vlsiffra is an Amaranth HDL Standard Cell Generator

IBM developer Anton Blanchard has written and released a standard cell generator in Amaranth HDL, dubbed vlsiffra, capable of hitting 2.7GHz on a 7nm process node.

"Vlsiffra is a generator of fast and efficient standard cell adders, multipliers, and multiply-adders," Anton explains. "It's written in Amaranth HDL, formally verified with Yosys. Verilator verification too. With OpenROAD and ASAP7 7nm a 32-bit 3-cycle multiplier hits 2.7GHz."

The project includes a range of configuration options, from the the number of bits - "any power of two likely works," Anton explains, "although Amaranth does start to slow down when building 64-bit multipliers" - to the choice of algorithm including Ripple for minimal area and Kogge-Stone for highest performance.

"My last attempt to name an Open Source project resulted in the impossible to Google for 'Microwatt' OpenPOWER VHDL core," Anton explains of the project's unusual but easy-to-search-for name. "Vlsiffra is a portmanteau of VLSI and siffra, the Swedish word for number."

Vlsiffra is available on GitHub now, under the permissive Apache 2.0 licence.

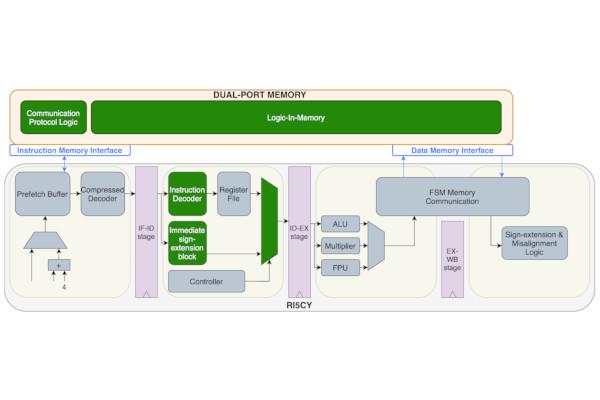

RISC-Vlim is a RISC-V Framework for Logic-in-Memory Architectures

Researchers from the Politecnico di Torin, University of Tor Vergata, and the University of Twente have developed a framework for the creation of RI5CY-based logic-in-memory microprocessors, including new LiM instructions for the RISC-V architecture itself, as a way of breaking through the "memory wall" performance barrier.

"Here we propose an RISC-V framework that supports logic-in-memory operations. We substitute data memory with a circuit capable of storing data and of performing in-memory computation," the team explains. "The framework is based on a standard memory interface, so different logic-in-memory architectures can be inserted inside the microprocessor, based both on CMOS and emerging technologies.

"The main advantage of this framework is the possibility of comparing the performance of different logic-in-memory solutions on code execution. We demonstrate the effectiveness of the framework using a CMOS volatile memory and a memory based on a new emerging technology, racetrack logic. The results demonstrate an improvement in algorithm execution speed and a reduction in energy consumption."

A paper detailing the framework, dubbed RISC-Vlim, is available under open-access terms following its publication in the journal Electronics; the framework, including the ISA and toolchain modifications, is available on GitHub under the permissive Solderpad Hardware Licence v0.51.

Charles Lohr's RISC-V Emulator Lives in a Single, 400-Line C Header

Electrical engineer Charles Lohr has been experimenting with the free and open-source RISC-V architecture, and the results are both unusual and impressive: a functional emulator written as a single 400-or-so-line C header file.

"I've been working really hard over the last few weeks on this little tiny RISC-V emulator. The really tiny part about is is that it doesn't have an MMU which is something that virtually all desktop modern processors have," Lohr explains of his work.

"The reason I wanted to do this was I wanted to see if I could run Linux on it. Something that was close to but not as simple as an ESP32-C3. And well the answer was. Yes. In fact I was able to write a really tiny RISC-V emulator. The actual emulator part all exists in this one function in this header file and it was only around 350, 400 lines of code. And it's able to run Linux and I'm able to have executables and whatever on it."

A demonstration of the emulator, which implements RV32IMA with Zifencei and Zicsr extensions, is available on YouTube; the emulator itself is available on GitHub under the permissive MIT, BSD three-clause, and Creative Commons Zero licences.

RISC-V Advanced Interrupt Architecture, Zicntr, Zihpm Enter Public Review Period

RISC-V International has announced public review periods for three key extensions: The Advanced Interrupt Architecture (AIA), Zicntr for base counters and timers, and Zihpm for hardware performance counters.

"We are delighted to announce the start of the public review period for the RISC-V Advanced Interrupt Architecture (AIA) specification, which contains both ISA and non-ISA components," John Hauser, vice-chair of the AIA Task Group, announced in the RISC-V ISA mailing list. "The RISC-V AIA specification is considered as frozen now as per the RISC-V International policies."

The RISC-V AIA aims to improve the interrupt-handling capabilities of the base RISC-V architecture with support for message-signalled interrupts (MSIs) from devices, direct control of device interrupts by a guest operating system running in virtual supervisor mode, intermixing of priorities, conditional delegation, and includes additional standard local interrupts for RISC-V harts.

The Zicntr and Zihpm ISA extensions, meanwhile, add standardised functionality for base counters and timers and for hardware performance counters respectively. These form part of the latest incarnation of the Unprivileged Specification, and are detailed in the RISC-V ISA manual.

Those interested in commenting on any of the extensions can find out how to do so in the Zicntr/Zihpm or AIA announcement posts; the former review period lasts until the 23th of December with the latter expiring on the 24th.

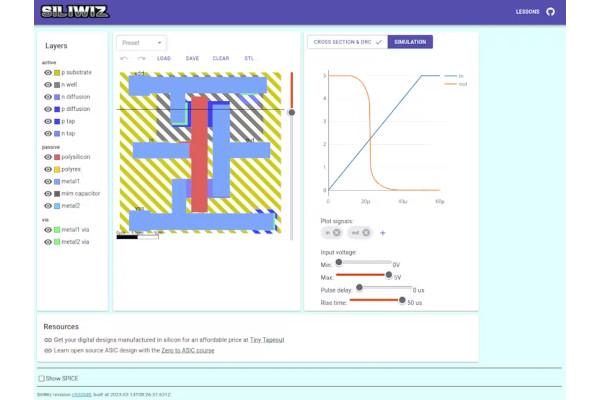

Matthew Venn's SiliWiz Aims to Drop the Barrier to Analogue Silicon Design Entry

Matthew Venn, creator of the Zero to ASIC Course and Tiny Tapeout programme, has shown off a new tool designed to lower the barrier to entry for analogue silicon design: SiliWiz.

"The problem with even the open-source ASIC tools is that it takes a while to learn how to draw the shapes," Matthew explains. "Then you've got to learn how to extract the circuit into a SPICE file, and then you've got to learn how to use that SPICE file to make a simulation.

"Then you've got to run the simulation, get the plot, and save it, and then you go make a change and you can't remember which graph you're comparing to what - you don't know what you did and how it changed."

In an effort to reduce these pain points and speed experimentation, Matthew has come up with SiliWiz. "SiliWiz combines the layout, the extraction, the cross-section, and simulation all into a single web page that we can use to explore and explain these fundamental concepts, and you don't even need to download anything."

A demonstration of SiliWiz is available on Matthew's YouTube channel, while the tool itself is currently only available under early-access terms to Tiny Tapeout submitters.

The PULP Platform Announces "The Incredible" HULK-V, a Low-Cost RISC-V SoC

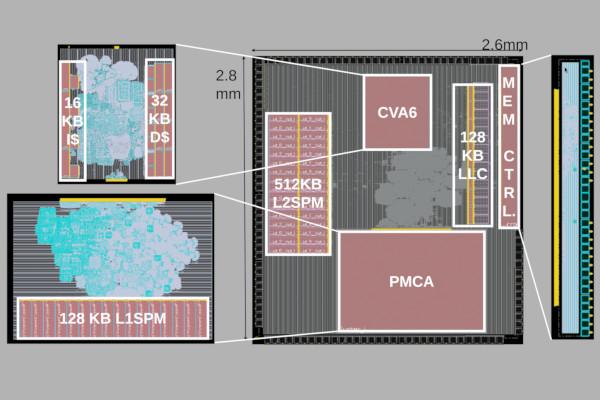

The PULP Platform has announced a new design, "The Incredible" HULK-V - a heterogeneous RISC-V system-on-chip capable of running Linux in a 250mW power envelope.

"We present HULK-V, an open-source heterogeneous Linux-capable RISC-V-based SoC coupling a 64-bit RISC-V processor with an 8-core Programmable Multi-Core Accelerator (PMCA), delivering up to 13.8 GOps, up to 157 GOps/W and accelerating the execution of complex DSP and ML tasks by up to 112x over the host processor," the team, including first author Luca Valente, explain.

"HULK-V leverages a lightweight, fully digital memory hierarchy based on HyperRAM IoT DRAM that exposes up to 512 MB of DRAM memory to the host CPU. Featuring HyperRAMs, HULK-V doubles the energy efficiency without significant performance loss compared to featuring power-hungry LPDDR memories, requiring expensive and large mixed-signal PHYs.

"HULK-V, implemented in GlobalFoundries 22nm FDX technology, is a fully digital ultra-low-cost SoC running a 64-bit Linux software stack with OpenMP host-to-PMCA offload within a power envelope of just 250mW," the researchers conclude.

The team's paper is available on Cornell's arXiv preprint server now

Kamakoti Veezhinathan Reflects on Building the SHAKTI Microprocessor

Kamakoti Veezhinathan has penned an article for the Communications of the ACM looking at the work that has gon into the IIT-Madras SHAKTI microprocessor - a project which launched back in 2014 as part of the "Atmanirbhar" effort to give India a native processor ecosystem.

"The SHAKTI initiative is aimed to create open source, industrial-grade processors and build associated components of a more extensive ecosystem," Kamakoti explains. "This ecosystem is beyond these processor designs. Today, the SHAKTI program offers a software stack, FPGA prototypes, interconnect fabrics, accelerators, device IPs, verification suites, and more under a permissive open source licence.

"Today the SHAKTI microprocessor-based FPGA is running well over a year at the Indira Gandhi Centre for Atomic Research. This implementation provides security toward obsolescence of processors. The industry will be adopting SHAKTI in the next two years. Many of the start-ups such as SecurWeave and Mindgrove have put in special efforts to make SHAKTI class of processors marketable."

The full article is available on the ACM website; more information is available on the project website.

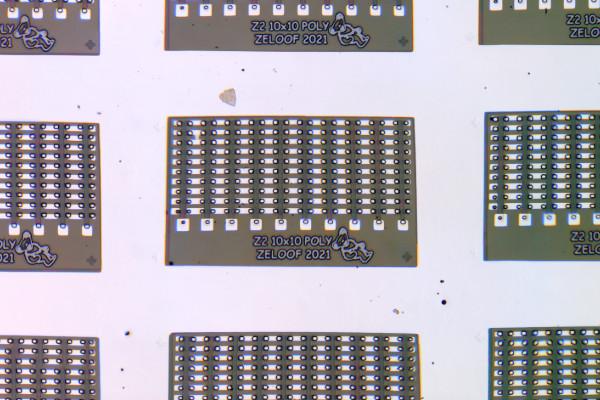

Wired Magazine Profiles Sam Zeloof and his Garage Silicon Fab

Popular technology magazine Wired has brought the concept of do-it-yourself processors to a broad audience, running a profile of Sam Zeloof - a man who is creating functional microchips using home-brew equipment installed in a garage.

"With a collection of salvaged and homemade equipment," Wired's Tom Simonite writes in the piece, "Zeloof produced a chip with 1,200 transistors. He had sliced up wafers of silicon, patterned them with microscopic designs using ultraviolet light, and dunked them in acid by hand, documenting the process on YouTube and his blog. 'Maybe it’s overconfidence, but I have a mentality that another human figured it out, so I can too, even if maybe it takes me longer,' he says."

Regular readers of El Correo Libre will remember Sam's achievement well - and the process which led up to it, including trial-and-error experimentation and the acquisition of a range of older fabrication equipment from auctions and closure sales. In the months since, Sam has been upgrading his home fab with an eye on more complicated chips on a 300nm node: "I want to push garage silicon further," he tells the magazine, "and open people’s minds to the possibility that we can do some of this stuff at home."

The full profile is available on the Wired website, with more information available on Sam's blog.

FOSSi News In Brief

- Tom Verbeure details the "particularly powerful" techmap command in Yosys, "the Swiss Army knife of digital logic manipulation."

- Matthew Venn closes Tiny Tapeout 2 with over 144 projects - including an implementation of the award-winning SERV core.

- Ted Fried releases MCL86, "to my knowledge the only open-source cycle-accurate Intel 8086 core available."

- The Linux Foundation, RISC-V International partner up for a new RISC-V Foundational Associate (RVFA) qualification.

- The CHIPS Alliance invites you to its Fall Technology Update, 15th December at 0830 PT.

- The RISC-V Summit 2022 is on right now.

- Intel announces changes to its Pathfinder for RISC-V development environment, including the "unification" of the Starter and Professional Editions.

Have feedback or news for inclusion in a future newsletter? Please send this to ecl@librecores.org.

Subscribe to get El Correo Libre direct to your inbox.